湖南6脚差分晶振

差分晶振的谐波失真探讨

差分晶振,谐波失真作为评价差分晶振性能的重要指标之一,其表现情况受到多样关注。首先,我们需要了解谐波失真的基本概念。在理想情况下,差分晶振的输出信号应该与输入信号保持一致,但由于电子设备的非线性特性,输出信号往往会发生形状变化,导致谐波成分增多,从而引起谐波失真。这种失真会使得输出信号的波形发生畸变,进而影响到信号的准确性和稳定性。差分晶振作为一种高精度、高稳定性的振荡器,其谐波失真情况通常被控制在较低的水平。然而,在实际应用中,由于各种因素的影响,如温度变化、电源电压波动等,差分晶振的谐波失真可能会发生变化。因此,对于差分晶振的设计和制造,需要充分考虑这些因素,并采取有效的措施来降低谐波失真。此外,对于差分晶振的使用者而言,了解并掌握差分晶振的谐波失真特性也是非常重要的。通过合理的电路设计和优化,可以进一步降低差分晶振的谐波失真,提高系统的整体性能。总的来说,差分晶振的谐波失真情况是一个复杂而重要的问题。

在实际应用中,我们需要通过不断的研究和实践,探索更加有效的降低谐波失真的方法,以提高差分晶振的性能和稳定性,为现代电子设备的发展提供有力的支持。 125m差分晶振-差分晶振选型,样品报价。湖南6脚差分晶振

差分晶振的频率范围:技术深度解析

差分晶振的频率范围究竟是多少呢?

首先,差分晶振的频率范围并非固定不变,而是根据具体的应用需求和设计来决定。常见的频率范围从几十千赫兹(kHz)到几千兆赫兹(GHz),显示出极大的灵活性和适应性。例如,一些常见的差分晶振频率范围可以是10MHz~250MHz,甚至更宽如10.0000——425.0000MHZ。

其次,差分晶振的频率精度也是选择时需要考虑的重要因素。频率稳定度(精度ppm)是衡量差分晶振性能的关键指标之一。一般来说,差分晶振的调整频差和温度频差可以在±25ppm到±100ppm之间。这意味着,即使在温度变化或工作条件改变的情况下,差分晶振也能保持相对稳定的频率输出。

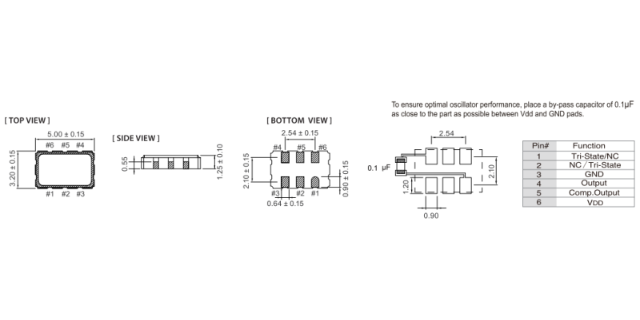

此外,差分晶振的电压和封装尺寸等参数也是选择时需要考虑的因素。工作电压通常在2.5V到3.3V之间,但也有一些产品支持更宽的电压范围,如2.25V、3.0V、3.6V等。封装尺寸方面,常见的有70*50、50*32、32*25、25*20、14x9.0等。

总的来说,差分晶振的频率范围是一个复杂而多变的参数,需要根据具体的应用需求来选择。在选择差分晶振时,除了考虑频率范围外,还需要考虑其相位噪声、电压、封装尺寸、工作温度以及频率稳定度等参数,以确保选择到适合的产品。 湖南6脚差分晶振差分晶振的可靠性如何?

差分晶振的负载效应对性能的影响

负载效应指的是差分晶振的输出端所连接的外部电路对其性能产生的影响。当差分晶振的输出端连接的负载电容、负载电阻等参数发生变化时,其输出频率和稳定性都可能受到影响。这是因为负载的变化会改变差分晶振内部的谐振条件,从而影响其工作状态。

首先,负载效应对差分晶振的输出频率具有明显影响。当负载电容或负载电阻增加时,差分晶振的输出频率可能会下降;反之,当负载减小时,输出频率可能上升。这种频率变化可能导致系统工作不正常,甚至引发故障。

其次,负载效应还会影响差分晶振的稳定性。稳定性是差分晶振的重要性能指标之一,它决定了输出频率的准确性和长期稳定性。负载的变化可能导致差分晶振的稳定性下降,使其输出频率产生漂移或抖动,进而影响整个系统的性能。

为了减小负载效应对差分晶振性能的影响,可以采取以下措施:首先,在设计电路时,应尽量选择与差分晶振匹配的负载电容和负载电阻,以保证其工作在比较好状态;其次,可以采用缓冲放大器或驱动电路来隔离外部电路对差分晶振的影响;,定期对差分晶振进行校准和维护,以确保其性能的稳定性和准确性。综上所述,差分晶振的负载效应对其性能具有重要影响。

LVDS(LowVoltageDifferentialSignaling,低电压差分信号)接口,又称为RS-644总线接口,是20世纪90年代提出的一种数据传输和接口技术。它克服了TTL电平方式在传输宽带高码率数据时功耗大、电磁干扰大的问题。采用低压和低电流驱动方式,实现了低噪声和低功耗,因此在液晶电视等需要高信号完整性和低抖动的系统中得到了广泛应用。CML(CurrentModeLogic,电流模式逻辑)则是一种常用于网络物理层传输和高速Serdes器件的接口技术。其理论极限速度可达10Gbit/s,功率更低,外部更简单。CML的输出电路形式是一个差分对,输出信号的摆幅与供电电压有关,耦合方式则根据接收器和发送器的电源配置来选择。LVPECL(LowVoltagePositiveEmitter-CoupledLogic,低电压正射极耦合逻辑)接口由ECL和PECL发展而来,使用3.3V电平。其输出结构为一对差分信号,通过电流源接地。LVPECL的差分输出端具有特定的传输阻抗和输出电平,使其在各种应用场景中都能保持稳定的性能。VML(VoltageModeLogic,电压模式逻辑)接口则具有其独特的电压特性和信号传输方式,为不同设备间的连接提供了灵活的选择。这四种接口技术各具特色,为现代电子设备提供了高效、稳定的数据传输方案。差分晶振的相位抖动如何?

差分晶振的LVDS、LVPECL、HCSL、CML模式介绍及其相互转换

差分晶振LVDS、LVPECL、HCSL和CML是常见的输出模式,每种模式都有其独特的特点和应用场景。LVDS,即低压差分信号,通过两个互补的信号线传输数据,提高抗干扰能力和传输距离,适用于高速数据传输和显示接口。而LVPECL则采用差分对放大器驱动射极跟随器,输出直流电流,常用于需要精确和稳定时钟信号的应用。HCSL,即高速电流转向逻辑,是一种低电压、低功耗的差分信号,通过控制电流方向传输数据,常用于系统内部的高速串行通信。CML,即电流模式逻辑,使用差分共发射极晶体管和集电极电阻,实现信号的摆幅,适用于需要快速响应和稳定性能的应用。在实际应用中,差分逻辑电平之间的转换是必不可少的。这通常通过在驱动器侧和接收器侧之间增加衰减电阻和偏置电路来实现,从而将一个差分逻辑转换为其他类型的差分逻辑,以满足不同系统的需求。差分逻辑电平匹配原则包括确保驱动器件的输出电压在负载器件的输入电压范围内,并保持一定的噪声容限,同时驱动器件还需满足负载器件对电流的需求。综上所述,差分晶振的LVDS、LVPECL、HCSL和CML模式各具特色,相互转换则是实现系统间互操作的关键。 差分晶振如何与FPGA连接?湖南6脚差分晶振

差分晶振的电压控制功能如何?湖南6脚差分晶振

差分晶振的调谐精度探讨

调谐精度是差分晶振性能评估的重要参数之一,其优劣对于通信、计算机等领域的应用至关重要。首先,我们需要明确差分晶振调谐精度的含义。简单来说,调谐精度就是差分晶振在特定工作条件下,其输出频率与设定频率之间的偏差大小。理想情况下,这个偏差值应尽可能小,以保证差分晶振的准确性和稳定性。在实际应用中,差分晶振的调谐精度受到多种因素的影响。首先,晶振本身的制造工艺和材料选择会直接影响其性能。质量的材料和精细的制造工艺能够减小晶振内部的误差,从而提高调谐精度。其次,环境因素如温度、湿度等也会对差分晶振的调谐精度产生影响。因此,在设计和使用差分晶振时,需要充分考虑这些环境因素,并采取相应的措施进行补偿和校正。为了提高差分晶振的调谐精度,科研人员和企业不断进行技术创新和工艺改进。例如,采用先进的温度补偿技术,可以减小温度变化对晶振性能的影响;优化电路设计和布线方式,可以减小电路中的噪声和干扰,从而提高差分晶振的精度和稳定性。总的来说,差分晶振的调谐精度是衡量其性能优劣的重要指标之一。 湖南6脚差分晶振

上一篇: 19.2M贴片晶振优势

下一篇: 有源40MHZ晶振怎么收费