1M晶振结构

降低晶振的相位噪声可以从多个方面入手:选择高质量晶体:选择具有高质量、晶格结构均匀、无缺陷的晶体,这有利于提高振荡频率的稳定性和降低相位噪声。优化晶体制备工艺:通过精密控制晶体生长和加工工艺,确保晶体的物理特性和结构质量,这有助于提高晶体的Q值,进而减小相位噪声。优化晶体外围电路:设计低噪声的放大器作为振荡电路的驱动源,减小放大器的噪声贡献;在晶振外围电路中尽量减小阻抗失配,保持信号的传输质量;采取有效的电磁屏蔽措施,减少外部环境对晶振电路的干扰。系统电路优化:通过合理设计系统电路,优化电磁兼容性,降低电磁辐射和电压波动,从而减少对晶振相位稳定性的影响。使用降噪滤波技术:在晶振输出信号之后,采用滤波技术对信号进行降噪处理,去除频谱中的噪声成分,提高信号的纯净度和稳定性。遵循以上方法,可以有效降低晶振的相位噪声,提高电路的稳定性和性能。深入了解晶振参数:掌握晶振性能的关键因素。1M晶振结构

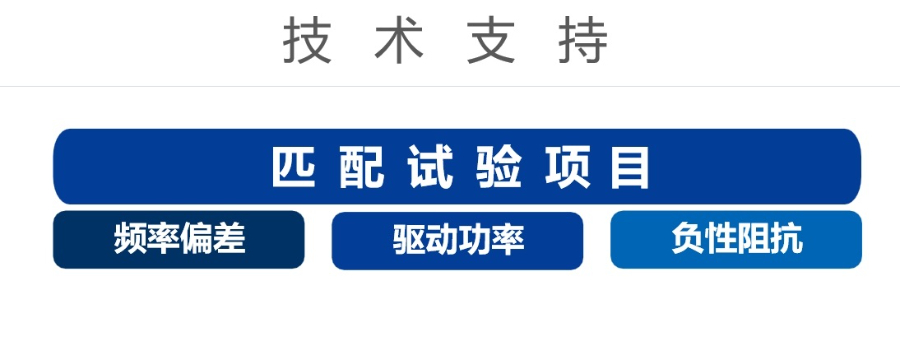

为了延长晶振的使用寿命,可以采取以下几个关键的措施:控制工作环境:确保晶振工作在适宜的温度范围内,通常是在-20°C到70°C之间。避免过热或过冷的环境,因为这会影响晶振的稳定性和寿命。保持工作环境干燥,避免湿度过高导致的腐蚀问题。尽可能减少或避免晶振受到机械冲击和振动,因为这些都可能损坏晶振的内部结构。正确的电源管理:为晶振提供稳定的电源电压,避免电压波动或超出其工作电压范围。在设计电路时,注意电源的滤波和去耦,以减少电源噪声对晶振的影响。正确的匹配:根据晶振的规格和要求,选择正确的负载电容和匹配电阻,以确保晶振能够稳定工作。注意晶振的驱动水平,避免过度驱动导致的损坏。减少电磁干扰:在设计中采取适当的电磁屏蔽和接地措施,以减少电磁干扰对晶振的影响。避免将晶振放置在靠近高噪声源的位置。定期检查和维护:定期检查晶振的性能,如频率稳定性、相位噪声等,以确保其正常工作。如有需要,及时更换损坏或性能下降的晶振。选择高质量的晶振:在购买晶振时,选择**品牌和高质量的产品,以确保其性能和寿命。1M晶振结构晶振选型-晶振的型号有哪些-晶振封装一览表。

晶振的相位噪声在频域上被用来定义数据偏移量。对于频率为f0的时钟信号而言,如果信号上不含抖动,那么信号的所有功率应集中在频率点f0处。然而,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,它们分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。相位噪声就是信号在某一特定频率处的功率分量,将这些分量连接成的曲线就是相位噪声曲线。它通常定义为在某一给定偏移处的dBc/Hz值,其中dBc是以dB为单位的该功率处功率与总功率的比值。例如,一个振荡器在某一偏移频率处的相位噪声可以定义为在该频率处1Hz带宽内的信号功率与信号总功率的比值。相位噪声对电路的影响主要体现在以下几个方面:频率稳定性:相位噪声的增加会导致振荡器的频率稳定性下降,进而影响整个电路的工作稳定性。通信质量:在通信系统中,相位噪声会影响信号的传输质量,增加误码率,降低通信的可靠性。系统性能:相位噪声还会影响电路的其他性能指标,如信噪比、动态范围等,进而影响整个系统的性能。因此,在电路设计中,需要采取一系列措施来降低晶振的相位噪声,以保证电路的稳定性和性能。例如,可以选择低噪声的晶振、优化电路布局、降低电源电压波动等。

晶振的抗冲击和振动能力是其性能的重要指标之一,对于确保其在各种复杂环境中的稳定运行至关重要。首先,晶振需要具备出色的抗振能力。在设备运行过程中,尤其是如汽车等移动设备,会持续受到振动的影响。这些振动可能导致晶振内部结构的微小变化,从而影响其稳定性和准确性。因此,晶振的设计和制造需要考虑如何减少振动对其性能的影响,如采用特殊的抗震结构、提高材料的抗振性能等。其次,晶振的抗冲击能力同样重要。在某些情况下,设备可能会受到意外的冲击,如跌落、碰撞等。这些冲击可能导致晶振受到严重的损坏,甚至完全失效。因此,晶振需要具备足够的抗冲击能力,以确保在受到冲击时仍能保持其稳定性和准确性。具体来说,不同类型的晶振具有不同的抗冲击和振动能力。例如,石英晶振虽然具有较高的稳定性和准确性,但其抗冲击和振动能力相对较弱,因此在一些特殊的应用中可能需要采用其他类型的晶振,如MEMS硅晶振。MEMS硅晶振采用先进的微机电系统技术制造,具有轻巧的设计和优良的抗冲击和振动能力,因此在一些对稳定性要求较高的应用中得到广泛应用。综上所述,晶振的抗冲击和振动能力是其性能的重要指标之一,需要在设计和制造过程中给予足够的重视。如何测量晶振的频率?

晶振的频率稳定性对电路性能具有明显影响。晶振作为电路中的时钟源,其频率的稳定性直接决定了电路的工作频率精度和时序控制的准确性。首先,晶振的频率稳定性影响电路的工作频率精度。如果晶振的频率稳定性较差,电路的工作频率将会出现偏差,这可能导致电路无法正常工作或性能下降。特别是在对频率精度要求较高的电路中,如通信设备、卫星导航系统等,晶振的频率稳定性更是至关重要。其次,晶振的频率稳定性影响电路的时序控制。时序控制是电路设计中的一个重要方面,它决定了电路中各个模块的工作顺序和时间间隔。如果晶振的频率稳定性不足,时序控制将会出现偏差,可能导致数据丢失、信号干扰等问题,影响电路的整体性能。此外,晶振的频率稳定性还影响电路的抗干扰能力。在复杂的电磁环境中,电路可能会受到各种干扰信号的影响。如果晶振的频率稳定性较差,电路可能会受到更多的干扰,导致性能下降甚至失效。因此,在设计电路时,需要选择频率稳定性好的晶振,以确保电路的稳定性和可靠性。同时,还需要注意环境温度、电源电压等因素对晶振频率稳定性的影响,采取相应的措施进行补偿和稳定。选择晶振时需要考虑的五个关键点。西藏22.1184M晶振

常见的晶振封装类型有哪些?1M晶振结构

晶振的负载电容是指在电路中跨接晶体两端的总的外界有效电容,这是晶振要正常震荡所需要的电容。它的大小主要影响负载谐振频率和等效负载谐振电阻。负载电容的确定一般依赖于晶振的数据手册或规格书,其中会明确标注出所需的负载电容值。此外,也可以通过计算公式来确定负载电容,公式为:晶振的负载电容Cf=[Cd*Cg/(Cd+Cg)]+Cic+△C,其中Cd、Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容)经验值为3至5pf。但需要注意的是,不同的IC和PCB材质可能会有所不同,因此需要根据实际情况适当调整。在应用中,一般外接电容是为了使晶振两端的等效电容等于或接近负载电容。如果负载电容不够准确,那么晶振的准确度就会受到影响。因此,在确定负载电容时,需要参考晶振的规格书或数据手册,并结合实际情况进行调整,以确保晶振的稳定性和准确度。1M晶振结构

上一篇: 宽电压32MHZ晶振温度系数

下一篇: 石家庄26MHZ晶振